目录

| 1.单片集成电路工艺 |

| 2.薄膜集成电路工艺 |

| 3.厚膜集成电路工艺 |

| 4.工艺特点 |

| 5.使用与注意事项 |

所谓集成电路工艺(integrated circuit technique

),就是把电路所需要的晶体管、二极管、电阻器和电容器等元件用一定工艺方式制作在一小块硅片、玻璃或陶瓷衬底上,再用适当的工艺进行互连,然后封装在一个管壳内,使整个电路的体积大大缩小,引出线和焊接点的数目也大为减少。集成电路的设想出现在50年代末和60年代初,是采用硅平面技术和薄膜与厚膜技术来实现的。电子集成技术按工艺方法分为以硅平面工艺为基础的单片集成电路、以薄膜技术为基础的薄膜集成电路和以丝网印刷技术为基础的厚膜集成电路。下面来了解一下这三种工艺的特点:

利用研磨、抛光、氧化、扩散、光刻、外延生长、蒸发等一整套平面工艺技术,在一小块硅单晶片上同时制造晶体管、二极管、电阻和电容等元件,并且采用一定的隔离技术使各元件在电性能上互相隔离。然后在硅片表面蒸发铝层并用光刻技术刻蚀成互连图形,使元件按需要互连成完整电路,制成半导体单片集成电路。

单片集成电路

随着单片集成电路从小、中规模发展到大规模、超大规模集成电路,平面工艺技术也随之得到发展。例如,扩散掺杂改用离子注入掺杂工艺;紫外光常规光刻发展到一整套微细加工技术,如采用电子束曝光制版、等离子刻蚀、反应离子铣等;外延生长又采用超高真空分子束外延技术;采用化学汽相淀积工艺制造多晶硅、二氧化硅和表面钝化薄膜;互连细线除采用铝或金以外,还采用了化学汽相淀积重掺杂多晶硅薄膜和贵金属硅化物薄膜,以及多层互连结构等工艺。

单片集成电路是独立实现单元电路功能,不需外接元器件的集成电路。要实现单片集成,需要解决一些不易微小型化的电阻、电容元件和功率器件的集成,以及各元件在电路性能上互相隔离的问题。

整个电路的晶体管、二极管、电阻、电容和电感等元件及其间的互连线,全部用厚度在1微米以下的金属、半导体、金属氧化物、多种金属混合相、合金或绝缘介质薄膜,并通过真空蒸发工艺、溅射工艺和电镀等工艺重叠构成。用这种工艺制成的集成电路称薄膜集成电路。主要工艺:

薄膜集成电路

①根据电路图先划分若干个功能部件图,然后用平面布图方法转化成基片上的平面电路布置图,再用照相制版方法制作出丝网印刷用的厚膜网路模板

②在基片上制造厚膜网路的主要工艺是印刷、烧结和调阻。常用的印刷方法是丝网印刷。

③在烧结过程中,有机粘合剂完全分解和挥发,固体粉料熔融,分解和化合,形成致密坚固的厚膜。厚膜的质量和性能与烧结过程和环境气氛密切相关,升温速度应当缓慢,以保证在玻璃流动以前有机物完全排除;烧结时间和峰值温度取决于所用浆料和膜层结构。为防止厚膜开裂,还应控制降温速度。常用的烧结炉是隧道窑。

④为使厚膜网路达到最佳性能,电阻烧成以后要进行调阻。常用调阻方法有喷砂、激光和电压脉冲调整等。

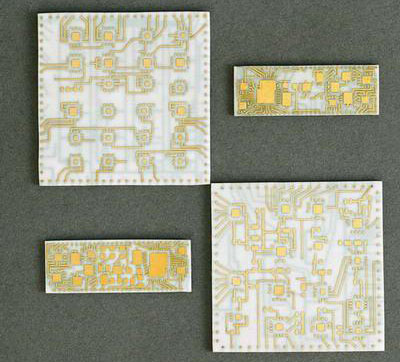

用丝网印刷工艺将电阻、介质和导体涂料淀积在氧化铝、氧化铍陶瓷或碳化硅衬底上。淀积过程是使用一细目丝网,制作各种膜的图案。这种图案用照相方法制成,凡是不淀积涂料的地方,均用乳胶阻住网孔。氧化铝基片经过清洗后印刷导电涂料,制成内连接线、电阻终端焊接区、芯片粘附区、电容器的底电极和导体膜。制件经干燥后,在750~950℃间的温度焙烧成形,挥发掉胶合剂,烧结导体材料,随后用印刷和烧成工艺制出电阻、电容、跨接、绝缘体和色封层。有源器件用低共熔焊、再流焊、低熔点凸点倒装焊或梁式引线等工艺制作,然后装在烧好的基片上,焊上引线便制成厚膜电路。

厚膜集成电路

厚膜电路的膜层厚度一般为 7~40微米。用厚膜工艺制备多层布线的工艺比较方便,多层工艺相容性好,可以大大提高二次集成的组装密度。此外,等离子喷涂、火焰喷涂、印贴工艺等都是新的厚膜工艺技术。与薄膜集成电路相仿,厚膜集成电路由于厚膜晶体管尚不能实用,实际上也是采用混合工艺。

单片集成电路和薄膜与厚膜集成电路这三种工艺方式各有特点,可以互相补充。通用电路和标准电路的数量大,可采用单片集成电路。需要量少的或是非标准电路,一般选用混合工艺方式,也就是采用标准化的单片集成电路,加上有源和无源元件的混合集成电路。厚膜、薄膜集成电路在某些应用中是互相交叉的。厚膜工艺所用工艺设备比较简易,电路设计灵活,生产周期短,散热良好,所以在高压、大功率和无源元件公差要求不太苛刻的电路中使用较为广泛。另外,由于厚膜电路在工艺制造上容易实现多层布线,在超出单片集成电路能力所及的较复杂的应用方面,可将大规模集成电路芯片组装成超大规模集成电路,也可将单功能或多功能单片集成电路芯片组装成多功能的部件甚至小的整机。

(1)集成电路在使用时不允许超过极限值,在电源电压变化不超过额定值的±10%时,电参数应符合规范值。电路在使用的电源接通与断开时,不得有瞬时电压产生,否则会使电路击穿。

(2)集成电路使用温度一般在–30~85℃之间,在系统安装时应尽量远离热源。

(3)集成电路如用手工焊接时,不得使用大于45W的电烙铁,连续焊接时间应不超过10S。

(4)对于MOS集成电路,要防止栅极静电感应击穿。

以上就是集成电路工艺的介绍了。目前单片集成电路除向更高集成度发展外,也正在向着大功率、线性、高频电路和模拟电路方面发展。不过,在微波集成电路、较大功率集成电路方面,薄膜、厚膜混合集成电路还具有优越性。在具体的选用上,往往将各类单片集成电路和厚膜、薄膜集成工艺结合在一起,特别如精密电阻网络和阻容网络基片粘贴于由厚膜电阻和导带组装成的基片上,装成一个复杂的完整的电路。必要时甚至可配接上个别超小型元件,组成部件或整机。

上一篇

CPLD实现数字滤波

下一篇

基于51单片机的温度相关文章

LM567为通用音调译码器,主要用于外界接电阻20比1范围,逻辑兼容输出具有吸收100mA电流能力。应用领域有振荡、调制、解调、和遥控编、译码电路。如电力线载波通信,对讲机亚音频译...

超声波检测(Ultrasonic Testing)缩写为UT,也叫超声检测,是利用超声波技术进行检测工作的,是五种常规无损检测方法的一种。无损检测是在不损坏工件或原材料工作状态的前...

集成电路是20世纪50年代后期一60年代发展起来的一种新型半导体器件,其应用遍及人类生活的方方面面。现代计算、交流、制造和交通系统,包括互联网,全都依赖于集成电路的存在。甚至很多学...

如今,集成电路持续向更小的外型尺寸发展,使得每个芯片可以封装更多的电路。这样增加了每单位面积容量,可以降低成本和增加功能-见摩尔定律,集成电路中的晶体管数量,每两年增加一倍。

集成电路测试是对集成电路或模块进行检测,通过测量对于集成电路的输出回应和预期输出比较,以确定或评估集成电路元器件功能和性能的过程,是验证设计、监控生产、保证质量、分析失效以及指导应...

数字集成电路是将元器件和连线集成于同一半导体芯片上而制成的数字逻辑电路或系统。数字集成电路构成了各种逻辑电路,如各种门电路、编译码器、触发器、计数器、寄存器等。它们广泛地应用在生活...